#### 4. CMOS-Inverter

- 4. **CMOS-Inverter**

- 4.1. Schaltungstechnik

- 4.2. n- und p-Wannen CMOS-Prozess

- 4.3. Latch-up Effekt

- 4.4. Twin-Well-Prozess

- 4.5. Silicon-on-Isolator (SOI)

Institut für Mikro-und Nanoelektronische Systeme

1

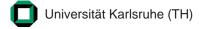

# 4.1. Schaltungstechnik: MOS-Transistoren (I)

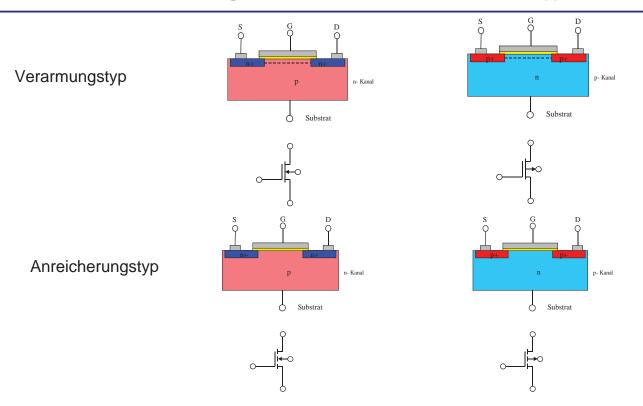

#### 4.1. Schaltungstechnik: MOSFET-Verarmungstyp

Eingangskennlinie

$$I_D = I_{D0} \left( 1 - \frac{U_{GS}}{U_{th}} \right)^2 \quad \Rightarrow \quad I_D = \frac{I_{D0}}{U_{th}^2} \left( U_{GS} - U_{th} \right)^2$$

Universität Karlsruhe (TH)

Institut für Mikro-und Nanoelektronische Systeme

3

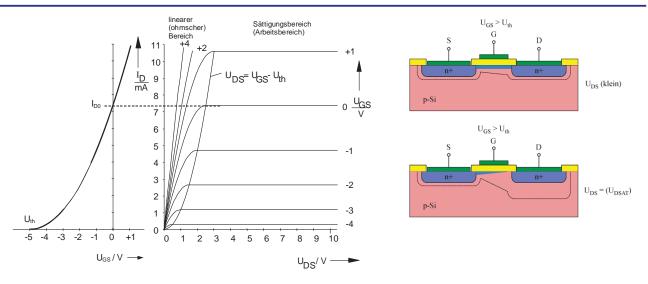

#### 4.1. Schaltungstechnik: MOSFET- Anreicherungstyp

Sättigungsbereich

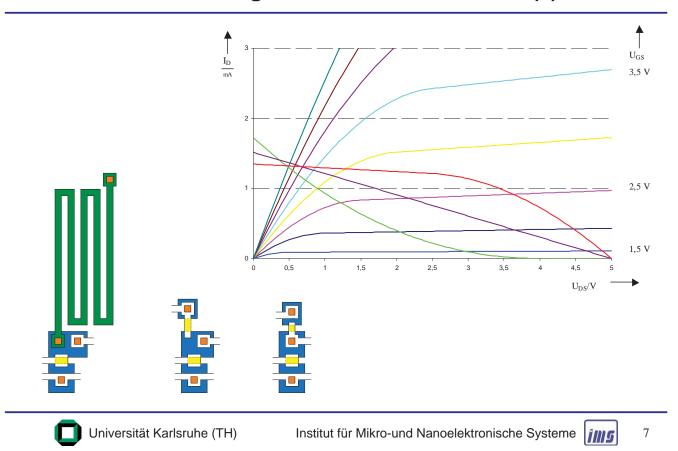

#### 4.1. Schaltungstechnik: MOSFET-Kennlinien

$$I_{D} = \begin{cases} 0 & U_{GS} \leq U_{th} \\ \beta \cdot \left( \left( U_{GS} - U_{th} \right) - \frac{U_{DS}^{2}}{2} \right) \left( 1 + \frac{U_{DS}}{U_{A}} \right) & linearer Bereich \\ \frac{\beta}{2} \cdot \left( U_{GS} - U_{th} \right)^{2} \left( 1 + \frac{U_{DS}}{U_{A}} \right) & S "attigungs bereich" \end{cases}$$

Steilheitskoeffizient:  $\beta = \beta'_n \frac{w}{l} = \mu_n C'_{ox} \frac{w}{l}$

$C_{ox} = C'_{ox} \cdot w \cdot I$ Kapazität des Gateoxids:

Institut für Mikro-und Nanoelektronische Systeme

5

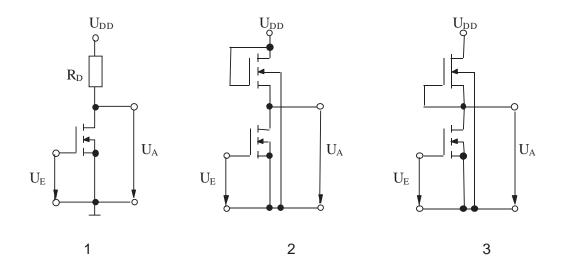

### 4.1. Schaltungstechnik: n-MOS-Inverter (I)

# 4.1. Schaltungstechnik: n-MOS-Inverter (II)

# 4.1. Schaltungstechnik: CMOS-Inverter

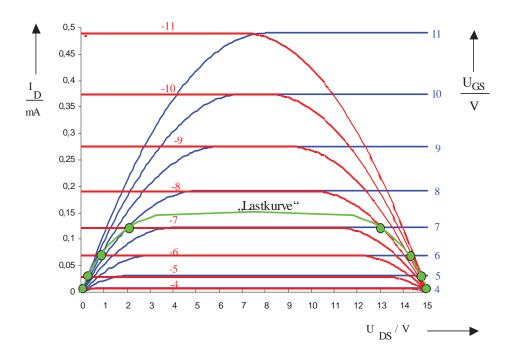

#### 4.1. Schaltungstechnik: CMOS-Kennlinienfeld

Universität Karlsruhe (TH)

Institut für Mikro-und Nanoelektronische Systeme

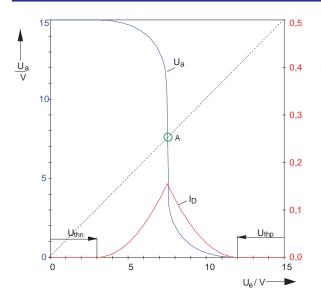

## 4.1. Schaltungstechnik: CMOS-Übertragungskennlinie

$$I_{D} = \beta \cdot \left[ (U_{GS} - U_{th}) \cdot U_{DS} - \frac{(U_{DS})^{2}}{2} \right] \quad (linearerBereich)$$

$$I_{D} = \frac{1}{2} \beta \cdot (U_{GS} - U_{th})^{2} \qquad (S\"{a}ttigungsbereich)$$

$$-I_{D} = \beta \cdot \left[ (U_{GS} - U_{th}) \cdot U_{DS} - \frac{(U_{DS})^{2}}{2} \right] \quad (linearerBereich)$$

$$-I_{D} = \frac{1}{2} \beta \cdot (U_{GS} - U_{th})^{2} \qquad (S\"{a}ttigungsbereich)$$

$$\beta_n = \mu_n C'_{ox} \frac{w_n}{l_n} = \beta$$

und  $\beta_p = \mu_p C'_{ox} \frac{w_p}{l_p} = \beta$

$mit \quad \mu_n \approx 3 \cdot \mu_p \ und \ der \ Annahme \ l_n = l_p \quad fo \ {\rm lg} \ t :$

$$w_p \approx 3 \cdot w_n$$

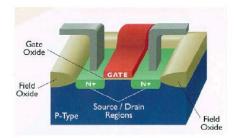

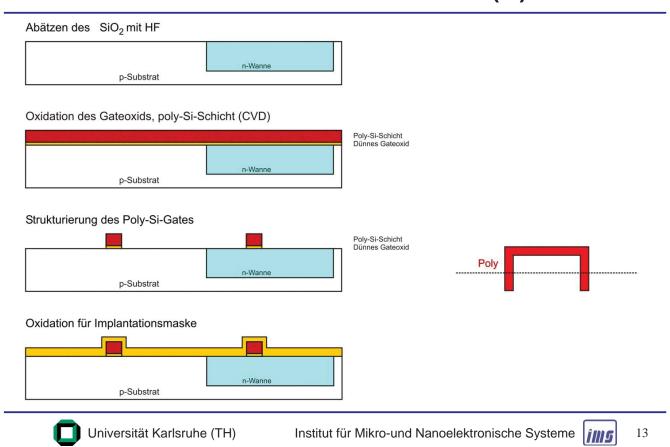

#### 4.2. n-Wannen-CMOS-Prozess (I)

#### **CMOS-Prozesse**

- n-Wannen-Prozess

- p-Wannen-Prozess

- Doppelwannen-Prozess

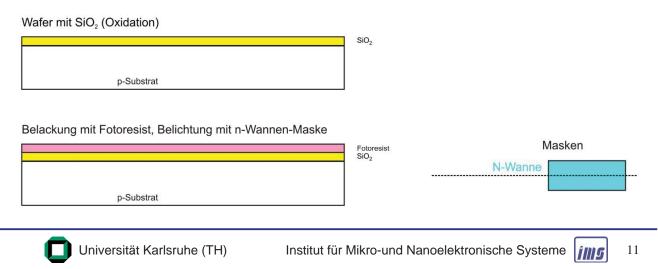

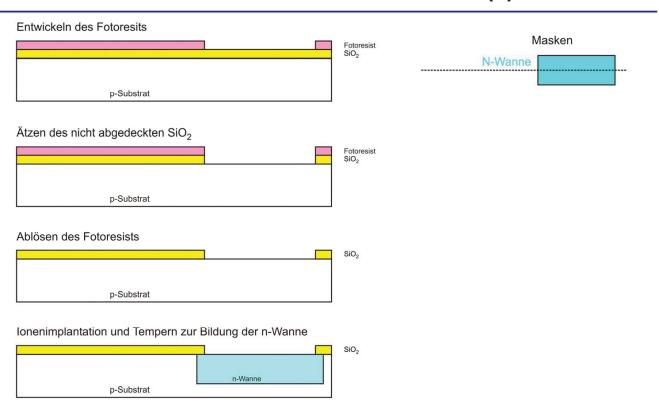

#### Herstellungsschritte im n-Wannen-CMOS-Prozess

### 4.2. n-Wannen-CMOS-Prozess (II)

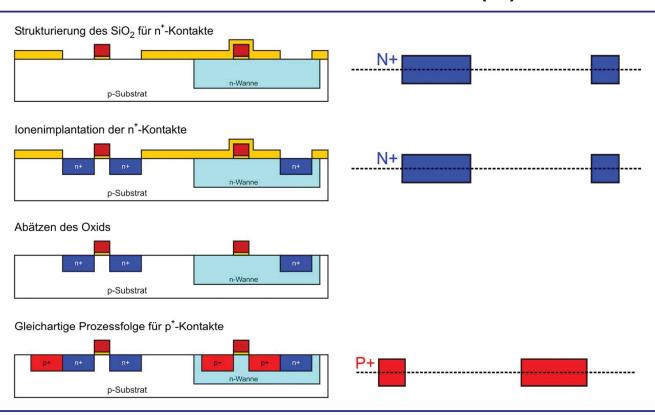

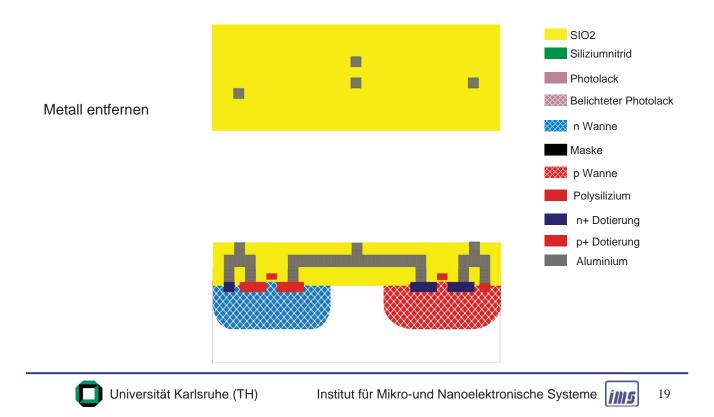

## 4.2. n-Wannen-CMOS-Prozess (III)

### 4.2. n-Wannen-CMOS-Prozess (IV)

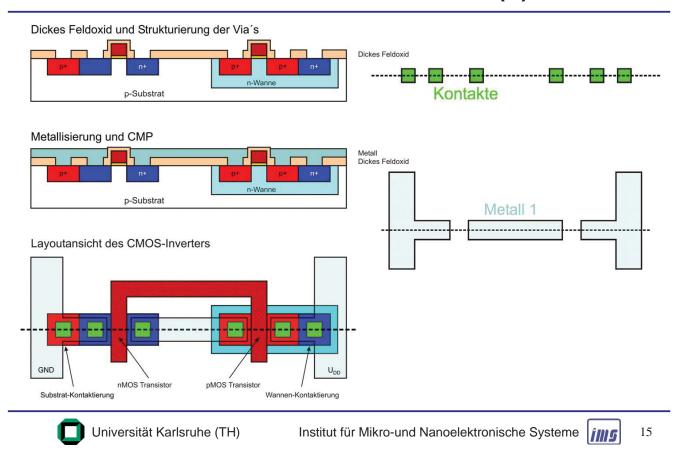

## 4.2. n-Wannen-CMOS-Prozess (V)

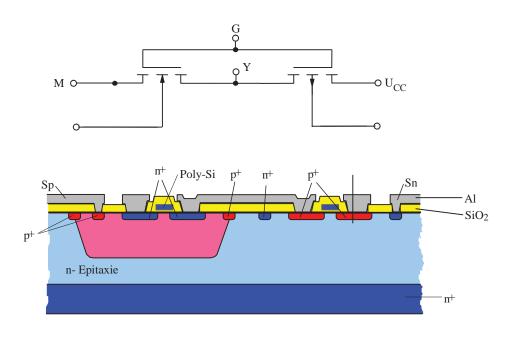

## 4.3. p-Wannen-CMOS-Prozess

16

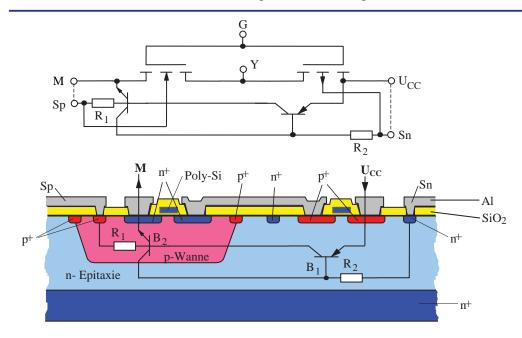

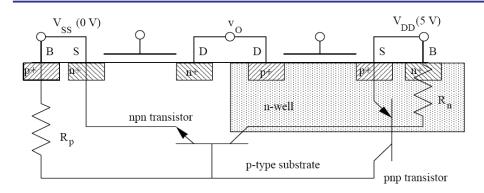

## 4.3. Latch-up Effekt: p-Wannen CMOS

Institut für Mikro-und Nanoelektronische Systeme

17

### 4.3. Latch-up Effekt: n-Wannen CMOS

#### Beseitigung des Latch-up Effektes

- Doppelwannen-Prozess (Twin-well)

- Schutzringe (guard rings)

- Graben-Isolation

- Silicon-on-Isolator (SOI)

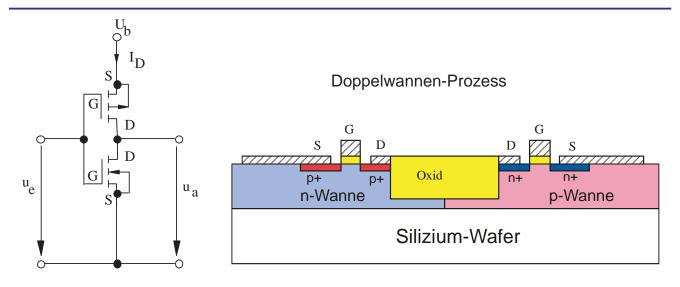

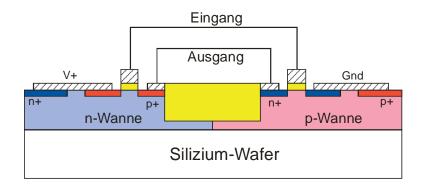

#### 4.4. Doppelwannen CMOS-Prozess (I)

### 4.4. Doppelwannen CMOS-Prozess (II)

#### Vorteile:

- n-Kanal und p-Kanal-Transistor können jeder für sich optimiert werden.

- hochohmiges Substrat reduziert die Anfälligkeit für den Latch-Up-Effekt

- Feldoxid reduziert die Leckströme zwischen den beiden Transistoren

#### Nachteile:

- Zusätzliche Prozessschritte und damit teurer als der p-well Prozess

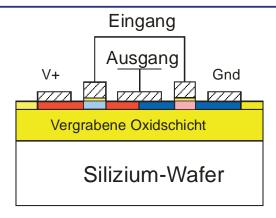

## 4.5. Silicon-on-Isolator (SOI)

#### Vorteile:

- Isolierendes Substrat , d.h: keine Substrateffekte

- Kein Latch-Up

- Keine parasitären Kapazitäten gegenüber Versorgungsspannung

#### Nachteile:

- Zusätzliche Prozessschritte

Institut für Mikro-und Nanoelektronische Systeme